Актуальні теми

#

Bonk Eco continues to show strength amid $USELESS rally

#

Pump.fun to raise $1B token sale, traders speculating on airdrop

#

Boop.Fun leading the way with a new launchpad on Solana.

Я трохи загубився у всіх абревіатурах і жаргоні тут, тому я попросив Клода пояснити це без використання будь-яких абревіатур, і тепер все це має сенс (tldr; пропускна здатність ⟹ простота):

Це захоплююча технічна дискусія про навчання великих мовних моделей у масштабі.

Суть розмови

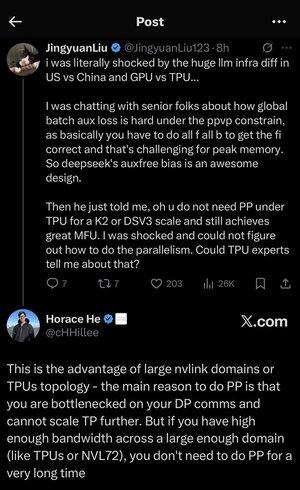

Цзін'юань Лю висловлює здивування, виявивши, що вам не потрібні певні складні методи оптимізації при використанні TPU (тензорні процесори - спеціалізовані чіпи штучного інтелекту Google) у порівнянні з графічними процесорами (графічними процесорами - зазвичай чіпами NVIDIA).

Пояснення ключових технічних понять:

Типи фурнітури:

•Графічний процесор (графічний процесор): спочатку розроблений для графіки, а зараз активно використовується для штучного інтелекту. NVIDIA домінує на цьому ринку.

•TPU (тензорний процесор): спеціально розроблені чіпи Google спеціально для машинного навчання.

Стратегії паралелізму:

Під час навчання масивних моделей штучного інтелекту вам потрібно розділити роботу на багато чіпів. Для цього є кілька способів:

1Паралелізм даних (DP): кожен чіп обробляє різні пакети даних з однією і тією ж копією моделі

2Тензорний паралелізм (TP): математичні операції моделі розподілені між мікросхемами

3Pipeline Parallelism (PP): різні шари моделі розміщуються на різних мікросхемах, створюючи конвеєр

Технічна задача, що обговорюється:

Проблема допоміжних втрат: при навчанні дуже великих моделей ви часто додаєте «допоміжні втрати» (додаткові тренувальні цілі) на проміжних рівнях, щоб допомогти градієнтам краще протікати через мережу. За обмежень PPVP (Pipeline Parallelism with Variable Partitioning) це стає складним, оскільки:

•Вам потрібно зробити "all f all b" (всі проходи вперед, потім всі проходи назад)

•Це складно для пікового використання пам'яті, оскільки вам потрібно зберігати проміжні результати

Інновація DeepSeek: вони розробили дизайн «допоміжного зміщення», який, очевидно, уникає потреби в цих допоміжних втратах, але при цьому ефективно тренується.

Несподіване одкровення:

Старший експерт розповів Jingyuan, що за допомогою TPU в масштабі K2 або DSV3 (це кластерні конфігурації з сотнями або тисячами чіпів) ви можете досягти відмінного MFU (Model FLOPs Utilization - в основному того, наскільки ефективно ви використовуєте обладнання) БЕЗ використання Pipeline Parallelism.

Чому це дивно?

• Паралелізм трубопроводів зазвичай вважається важливим для великомасштабного навчання

•Це складна техніка, яка потребує ретельної оптимізації

•Можливість уникнути цього значно спрощує все

Пояснення Горація:

Він пояснює, ЧОМУ це можливо за допомогою ТПУ:

Перевага в пропускній здатності: TPU та високоякісні кластери NVIDIA (наприклад, NVL72 - остання конфігурація NVIDIA з 72 графічними процесорами та з'єднаннями NVLink) мають настільки високу пропускну здатність між чіпами, що вони можуть впоратися з вимогами до зв'язку без Pipeline Parallelism.

Ключовий інсайт:

•Паралелізм конвеєра насамперед потрібен, коли ви «вузьке місце в комунікаціях DP» (обмежене швидкістю зв'язку під час паралельного навчання даних)

•Якщо у вас достатньо пропускної здатності в достатньо великому домені (взаємопов'язаному кластері), ви можете просто використовувати простіші стратегії паралелізму

• Це працює «дуже довго» - це означає, що ви можете тренувати навіть дуже великі моделі, не перевищуючи межі можливостей

Інтуїція:

Думайте про це як про систему автомагістралей:

• Традиційні кластери графічних процесорів схожі на вузькі дороги між містами, тому вам потрібна складна маршрутизація (Pipeline Parallelism), щоб уникнути заторів

• Кластери TPU або графічні процесори, підключені до NVLink, схожі на величезні супермагістралі – ви можете просто надсилати все напряму без вигадливої маршрутизації

Це дуже важливо, тому що Pipeline Parallelism складний у впровадженні, налагодженні та оптимізації. Можливість уникнути його, досягнувши при цьому високої ефективності, робить весь тренувальний процес набагато простішим і надійнішим.

Дискусія підкреслює, як прогрес у технології апаратного з'єднання («дороги» між чіпами) може докорінно змінити програмні стратегії, необхідні для ефективного навчання ШІ.

3,46K

Найкращі

Рейтинг

Вибране