Tendencias del momento

#

Bonk Eco continues to show strength amid $USELESS rally

#

Pump.fun to raise $1B token sale, traders speculating on airdrop

#

Boop.Fun leading the way with a new launchpad on Solana.

Me perdí un poco en todos los acrónimos y jerga aquí, así que hice que Claude lo explicara sin usar acrónimos y ahora todo tiene perfecto sentido (resumen; ancho de banda ⟹ simplicidad):

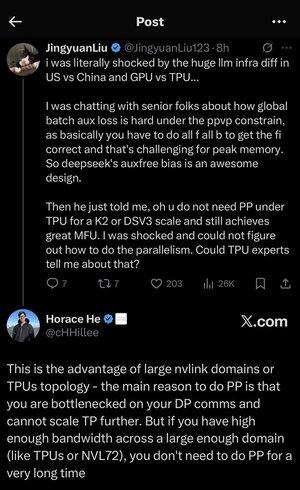

Esta es una fascinante discusión técnica sobre el entrenamiento de modelos de lenguaje grandes a gran escala.

La Conversación Central

Jingyuan Liu expresa sorpresa al descubrir que no necesitas ciertas técnicas de optimización complejas al usar TPUs (Unidades de Procesamiento Tensorial - los chips de IA especializados de Google) en comparación con GPUs (Unidades de Procesamiento Gráfico - típicamente chips de NVIDIA).

Conceptos Técnicos Clave Explicados:

Tipos de Hardware:

•GPU (Unidad de Procesamiento Gráfico): Originalmente diseñada para gráficos, ahora se utiliza mucho para IA. NVIDIA domina este mercado.

•TPU (Unidad de Procesamiento Tensorial): Chips diseñados a medida por Google específicamente para aprendizaje automático.

Estrategias de Paralelismo:

Al entrenar modelos de IA masivos, necesitas dividir el trabajo entre muchos chips. Hay varias formas de hacerlo:

1. Paralelismo de Datos (DP): Cada chip procesa diferentes lotes de datos con la misma copia del modelo.

2. Paralelismo Tensorial (TP): Las operaciones matemáticas del modelo se dividen entre chips.

3. Paralelismo en Pipeline (PP): Diferentes capas del modelo se colocan en diferentes chips, creando un pipeline.

El Desafío Técnico que se Está Discutiendo:

El problema de la pérdida auxiliar: Al entrenar modelos muy grandes, a menudo agregas "pérdidas auxiliares" (objetivos de entrenamiento adicionales) en capas intermedias para ayudar a que los gradientes fluyan mejor a través de la red. Bajo las restricciones de PPVP (Paralelismo en Pipeline con Particionamiento Variable), esto se vuelve complejo porque:

•Necesitas hacer "todo f todo b" (todas las pasadas hacia adelante, luego todas las pasadas hacia atrás).

•Esto es un desafío para el uso máximo de memoria porque tienes que almacenar resultados intermedios.

La innovación de DeepSeek: Desarrollaron un diseño de "sesgo sin pérdidas auxiliares" que aparentemente evita la necesidad de estas pérdidas auxiliares mientras sigue entrenando de manera efectiva.

La Revelación Sorprendente:

El experto senior le dijo a Jingyuan que con TPUs a escala K2 o DSV3 (estas son configuraciones de clúster con cientos o miles de chips), puedes lograr una excelente MFU (Utilización de FLOPs del Modelo - básicamente cuán eficientemente estás utilizando el hardware) SIN usar Paralelismo en Pipeline.

¿Por qué es esto sorprendente?

•El Paralelismo en Pipeline se considera típicamente esencial para el entrenamiento a gran escala.

•Es una técnica compleja que requiere una optimización cuidadosa.

•Poder evitarlo simplifica todo significativamente.

La Explicación de Horace He:

Él explica POR QUÉ esto es posible con TPUs:

La ventaja de ancho de banda: Los TPUs y los clústeres de NVIDIA de alta gama (como NVL72 - la última configuración de 72 GPUs de NVIDIA con interconexiones NVLink) tienen un ancho de banda tan alto entre chips que pueden manejar los requisitos de comunicación sin Paralelismo en Pipeline.

La clave de la percepción:

•El Paralelismo en Pipeline es principalmente necesario cuando estás "bloqueado en las comunicaciones de DP" (limitado por la rapidez con la que puedes comunicarte durante el entrenamiento paralelo de datos).

•Si tienes suficiente ancho de banda a través de un dominio lo suficientemente grande (clúster interconectado), puedes usar simplemente estrategias de paralelismo más simples.

•Esto funciona "durante mucho tiempo" - lo que significa que puedes entrenar incluso modelos muy grandes sin alcanzar los límites.

La Intuición:

Piénsalo como un sistema de carreteras:

•Los clústeres de GPU tradicionales son como tener carreteras estrechas entre ciudades, por lo que necesitas enrutamiento complejo (Paralelismo en Pipeline) para evitar atascos.

•Los clústeres de TPU o GPUs conectadas por NVLink son como tener supercarreteras masivas - puedes enviar todo directamente sin enrutamiento complicado.

Esto es un gran problema porque el Paralelismo en Pipeline es complejo de implementar, depurar y optimizar. Poder evitarlo mientras aún logras alta eficiencia hace que todo el proceso de entrenamiento sea mucho más simple y confiable.

La discusión destaca cómo los avances en la tecnología de interconexión de hardware (las "carreteras" entre chips) pueden cambiar fundamentalmente las estrategias de software necesarias para un entrenamiento de IA eficiente.

3,47K

Parte superior

Clasificación

Favoritos