Trend-Themen

#

Bonk Eco continues to show strength amid $USELESS rally

#

Pump.fun to raise $1B token sale, traders speculating on airdrop

#

Boop.Fun leading the way with a new launchpad on Solana.

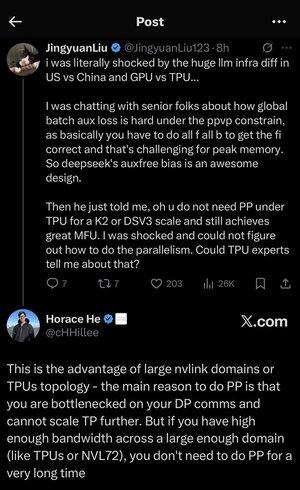

Ich habe mich ein wenig in all den Abkürzungen und dem Fachjargon hier verloren, also ließ ich Claude es mir ohne Abkürzungen erklären und jetzt macht alles perfekten Sinn (tl;dr; Bandbreite ⟹ Einfachheit):

Dies ist eine faszinierende technische Diskussion über das Training großer Sprachmodelle im großen Maßstab.

Das Kern-Gespräch

Jingyuan Liu äußert Überraschung darüber, dass man bestimmte komplexe Optimierungstechniken nicht benötigt, wenn man TPUs (Tensor Processing Units - Googles spezialisierte KI-Chips) im Vergleich zu GPUs (Graphics Processing Units - typischerweise NVIDIA-Chips) verwendet.

Wichtige technische Konzepte erklärt:

Hardwaretypen:

•GPU (Graphics Processing Unit): Ursprünglich für Grafiken entwickelt, jetzt stark für KI genutzt. NVIDIA dominiert diesen Markt.

•TPU (Tensor Processing Unit): Googles maßgeschneiderte Chips speziell für maschinelles Lernen.

Parallelitätsstrategien:

Beim Training massiver KI-Modelle muss man die Arbeit auf viele Chips aufteilen. Es gibt mehrere Möglichkeiten, dies zu tun:

1. Datenparallelismus (DP): Jeder Chip verarbeitet unterschiedliche Datenbatches mit derselben Modellkopie.

2. Tensorparallelismus (TP): Die mathematischen Operationen des Modells werden auf Chips aufgeteilt.

3. Pipeline-Parallelismus (PP): Verschiedene Schichten des Modells werden auf unterschiedlichen Chips platziert, wodurch eine Pipeline entsteht.

Die technische Herausforderung, die diskutiert wird:

Das Problem des Hilfsverlusts: Beim Training sehr großer Modelle fügt man oft "Hilfsverluste" (zusätzliche Trainingsziele) in Zwischenebenen hinzu, um den Fluss der Gradienten durch das Netzwerk zu verbessern. Unter den PPVP (Pipeline-Parallelismus mit variabler Partitionierung) Einschränkungen wird dies komplex, weil:

•Man muss "alle f alle b" (alle Vorwärtsdurchläufe, dann alle Rückwärtsdurchläufe) durchführen.

•Das ist herausfordernd für die Spitzen-Speichernutzung, da man Zwischenresultate speichern muss.

Die Innovation von DeepSeek: Sie entwickelten ein "auxfree bias"-Design, das anscheinend diese Hilfsverluste vermeidet und dennoch effektiv trainiert.

Die überraschende Offenbarung:

Der erfahrene Experte sagte Jingyuan, dass man mit TPUs im K2- oder DSV3-Maßstab (das sind Clusterkonfigurationen mit Hunderten oder Tausenden von Chips) eine hervorragende MFU (Model FLOPs Utilization - im Grunde, wie effizient man die Hardware nutzt) erreichen kann, OHNE Pipeline-Parallelismus zu verwenden.

Warum ist das überraschend?

•Pipeline-Parallelismus wird typischerweise als wesentlich für das Training im großen Maßstab angesehen.

•Es ist eine komplexe Technik, die sorgfältige Optimierung erfordert.

•Es zu vermeiden, vereinfacht alles erheblich.

Horace He's Erklärung:

Er erklärt, WARUM dies mit TPUs möglich ist:

Der Bandbreitenvorteil: TPUs und hochmoderne NVIDIA-Cluster (wie NVL72 - die neueste 72-GPU-Konfiguration von NVIDIA mit NVLink-Interconnects) haben eine so hohe Bandbreite zwischen den Chips, dass sie die Kommunikationsanforderungen ohne Pipeline-Parallelismus bewältigen können.

Der entscheidende Einblick:

•Pipeline-Parallelismus wird hauptsächlich benötigt, wenn man "bei DP-Kommunikationen im Engpass ist" (beschränkt durch die Geschwindigkeit, mit der man während des datenparallelen Trainings kommunizieren kann).

•Wenn man genügend Bandbreite über ein großes genug Gebiet (vernetztes Cluster) hat, kann man einfach einfachere Parallelitätsstrategien verwenden.

•Das funktioniert "sehr lange" - das bedeutet, man kann sogar sehr große Modelle trainieren, ohne die Grenzen zu erreichen.

Die Intuition:

Denken Sie an ein Autobahnsystem:

•Traditionelle GPU-Cluster sind wie enge Straßen zwischen Städten, sodass man komplexe Routenführung (Pipeline-Parallelismus) benötigt, um Staus zu vermeiden.

•TPU-Cluster oder NVLink-verbundene GPUs sind wie riesige Autobahnen - man kann einfach alles direkt senden, ohne ausgeklügelte Routenführung.

Das ist ein großes Ding, denn Pipeline-Parallelismus ist komplex zu implementieren, zu debuggen und zu optimieren. Es zu vermeiden, während man dennoch hohe Effizienz erreicht, macht den gesamten Trainingsprozess viel einfacher und zuverlässiger.

Die Diskussion hebt hervor, wie Fortschritte in der Hardware-Interconnect-Technologie (die "Straßen" zwischen den Chips) die Softwarestrategien, die für effizientes KI-Training benötigt werden, grundlegend verändern können.

3,47K

Top

Ranking

Favoriten