Populære emner

#

Bonk Eco continues to show strength amid $USELESS rally

#

Pump.fun to raise $1B token sale, traders speculating on airdrop

#

Boop.Fun leading the way with a new launchpad on Solana.

Jeg gikk meg litt vill i alle akronymene og sjargongen her, så jeg fikk Claude til å forklare det uten å bruke noen akronymer, og nå gir det hele perfekt mening (tldr; båndbredde ⟹ enkelhet):

Dette er en fascinerende teknisk diskusjon om trening av store språkmodeller i stor skala.

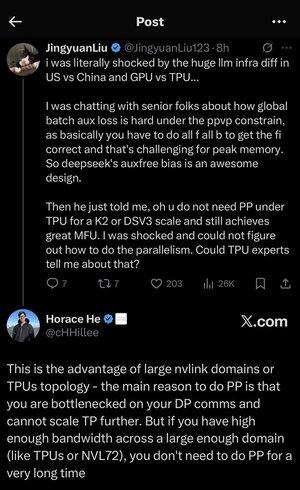

Kjernesamtalen

Jingyuan Liu uttrykker overraskelse over å oppdage at du ikke trenger visse komplekse optimaliseringsteknikker når du bruker TPU-er (Tensor Processing Units - Googles spesialiserte AI-brikker) kontra GPUer (Graphics Processing Units - vanligvis NVIDIAs brikker).

Viktige tekniske konsepter forklart:

Maskinvare typer:

•GPU (Graphics Processing Unit): Opprinnelig designet for grafikk, nå mye brukt for AI. NVIDIA dominerer dette markedet.

•TPU (Tensor Processing Unit): Googles spesialdesignede brikker spesielt for maskinlæring.

Parallellisme strategier:

Når du trener massive AI-modeller, må du dele arbeidet på tvers av mange brikker. Det er flere måter å gjøre dette på:

1Dataparallellitet (DP): Hver brikke behandler forskjellige datagrupper med samme modellkopi

2Tensorparallellitet (TP): Modellens matematiske operasjoner er delt på brikker

3Pipeline Parallelism (PP): Ulike lag av modellen er plassert på forskjellige brikker, og skaper en rørledning

Den tekniske utfordringen som diskuteres:

Hjelpetapsproblemet: Når du trener veldig store modeller, legger du ofte til "hjelpetap" (ekstra treningsmål) på mellomlag for å hjelpe gradienter til å flyte bedre gjennom nettverket. Under PPVP-begrensninger (Pipeline Parallelism with Variable Partitioning) blir dette komplisert fordi:

•Du må gjøre "alle f alle b" (alle foroverpasseringer, deretter alle bakoverpasseringer)

•Dette er utfordrende for topp minnebruk fordi du må lagre mellomliggende resultater

DeepSeeks innovasjon: De utviklet et "auxfree bias"-design som tilsynelatende unngår å trenge disse hjelpetapene mens de fortsatt trener effektivt.

Den overraskende avsløringen:

Senioreksperten fortalte Jingyuan at med TPU-er i K2- eller DSV3-skala (dette er klyngekonfigurasjoner med hundrevis eller tusenvis av brikker), kan du oppnå utmerket MFU (Model FLOPs Utilization - i utgangspunktet hvor effektivt du bruker maskinvaren) UTEN å bruke Pipeline Parallelity.

Hvorfor er dette overraskende?

•Pipeline-parallellitet anses vanligvis som avgjørende for opplæring i stor skala

•Det er en kompleks teknikk som krever nøye optimalisering

•Å kunne unngå det forenkler alt betydelig

Horace er forklaring:

Han forklarer HVORFOR dette er mulig med TPU-er:

Båndbreddefordelen: TPU-er og avanserte NVIDIA-klynger (som NVL72 - NVIDIAs nyeste 72-GPU-konfigurasjon med NVLink-sammenkoblinger) har så høy båndbredde mellom brikker at de kan håndtere kommunikasjonskravene uten Pipeline Parallelity.

Den viktigste innsikten:

•Pipeline-parallellitet er først og fremst nødvendig når du er "flaskehals på DP-kommunikasjon" (begrenset av hvor raskt du kan kommunisere under parallell datatrening)

•Hvis du har nok båndbredde over et stort nok domene (sammenkoblet klynge), kan du bare bruke enklere parallellitetsstrategier

•Dette fungerer "i veldig lang tid" - noe som betyr at du kan trene selv veldig store modeller uten å treffe grensene

Intuisjonen:

Tenk på det som et motorveisystem:

•Tradisjonelle GPU-klynger er som å ha smale veier mellom byer, så du trenger kompleks ruting (Pipeline Parallelity) for å unngå trafikkork

•TPU-klynger eller NVLink-tilkoblede GPUer er som å ha massive motorveier – du kan bare sende alt direkte uten fancy ruting

Dette er en stor sak fordi Pipeline Parallelism er komplisert å implementere, feilsøke og optimalisere. Å kunne unngå det samtidig som man oppnår høy effektivitet gjør hele opplæringsprosessen mye enklere og mer pålitelig.

Diskusjonen fremhever hvordan fremskritt innen maskinvaresammenkoblingsteknologi ("veiene" mellom brikker) fundamentalt kan endre programvarestrategiene som trengs for effektiv AI-opplæring.

3,46K

Topp

Rangering

Favoritter