Populaire onderwerpen

#

Bonk Eco continues to show strength amid $USELESS rally

#

Pump.fun to raise $1B token sale, traders speculating on airdrop

#

Boop.Fun leading the way with a new launchpad on Solana.

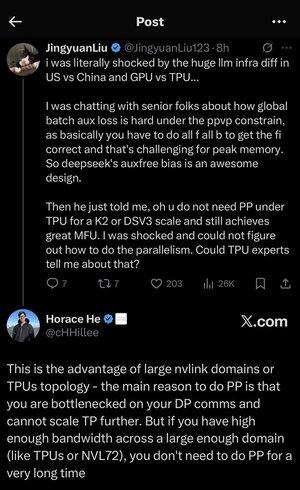

Ik raakte een beetje verdwaald in al deze afkortingen en jargon hier, dus vroeg ik Claude het uit te leggen zonder afkortingen en nu maakt het allemaal perfect sense (tldr; bandbreedte ⟹ eenvoud):

Dit is een fascinerende technische discussie over het trainen van grote taalmodellen op schaal.

De Kern Conversatie

Jingyuan Liu uit zijn verbazing over het ontdekken dat je bepaalde complexe optimalisatietechnieken niet nodig hebt bij het gebruik van TPU's (Tensor Processing Units - Google's gespecialiseerde AI-chips) in vergelijking met GPU's (Graphics Processing Units - typisch de chips van NVIDIA).

Belangrijke Technische Concepten Uitleg:

Hardware Types:

•GPU (Graphics Processing Unit): Oorspronkelijk ontworpen voor graphics, nu veel gebruikt voor AI. NVIDIA domineert deze markt.

•TPU (Tensor Processing Unit): Google's op maat ontworpen chips specifiek voor machine learning.

Parallelisme Strategieën:

Bij het trainen van enorme AI-modellen moet je het werk over veel chips verdelen. Er zijn verschillende manieren om dit te doen:

1Data Parallelisme (DP): Elke chip verwerkt verschillende batches gegevens met dezelfde modelkopie.

2Tensor Parallelisme (TP): De wiskundige bewerkingen van het model worden verdeeld over chips.

3Pipeline Parallelisme (PP): Verschillende lagen van het model worden op verschillende chips geplaatst, waardoor een pijplijn ontstaat.

De Technische Uitdaging Die Wordt Besproken:

Het probleem van de auxiliaire verlies: Bij het trainen van zeer grote modellen voeg je vaak "auxiliaire verliezen" (aanvullende trainingsdoelen) toe op tussenliggende lagen om de gradiënten beter door het netwerk te laten stromen. Onder PPVP (Pipeline Parallelism with Variable Partitioning) beperkingen wordt dit complex omdat:

•Je moet "alle f alle b" doen (alle voorwaartse passes, dan alle achterwaartse passes).

•Dit is uitdagend voor het piekgeheugengebruik omdat je tussenresultaten moet opslaan.

De innovatie van DeepSeek: Ze ontwikkelden een "auxfree bias" ontwerp dat blijkbaar het nodig hebben van deze auxiliaire verliezen vermijdt terwijl het nog steeds effectief traint.

De Verrassende Openbaring:

De senior expert vertelde Jingyuan dat je met TPU's op K2 of DSV3 schaal (dit zijn clusterconfiguraties met honderden of duizenden chips) uitstekende MFU (Model FLOPs Utilization - in wezen hoe efficiënt je de hardware gebruikt) kunt bereiken ZONDER Pipeline Parallelisme te gebruiken.

Waarom is dit verrassend?

•Pipeline Parallelisme wordt doorgaans als essentieel beschouwd voor training op grote schaal.

•Het is een complexe techniek die zorgvuldige optimalisatie vereist.

•Het kunnen vermijden ervan vereenvoudigt alles aanzienlijk.

De Uitleg van Horace He:

Hij legt uit WAAROM dit mogelijk is met TPU's:

Het bandbreedtevoordeel: TPU's en high-end NVIDIA-clusters (zoals NVL72 - NVIDIA's nieuwste 72-GPU-configuratie met NVLink-interconnects) hebben zo'n hoge bandbreedte tussen chips dat ze de communicatievereisten kunnen afhandelen zonder Pipeline Parallelisme.

De belangrijkste inzicht:

•Pipeline Parallelisme is voornamelijk nodig wanneer je "vastloopt op DP-communicatie" (beperkt door hoe snel je kunt communiceren tijdens data parallel training).

•Als je genoeg bandbreedte hebt over een groot genoeg domein (onderling verbonden cluster), kun je gewoon eenvoudigere parallelisme strategieën gebruiken.

•Dit werkt "voor een zeer lange tijd" - wat betekent dat je zelfs zeer grote modellen kunt trainen zonder de limieten te bereiken.

De Intuïtie:

Denk aan het als een snelwegsysteem:

•Traditionele GPU-clusters zijn als het hebben van smalle wegen tussen steden, dus je hebt complexe routering (Pipeline Parallelisme) nodig om verkeersopstoppingen te vermijden.

•TPU-clusters of NVLink-verbonden GPU's zijn als het hebben van enorme snelwegen - je kunt alles gewoon rechtstreeks verzenden zonder fancy routering.

Dit is een grote zaak omdat Pipeline Parallelisme complex is om te implementeren, debuggen en optimaliseren. Het kunnen vermijden ervan terwijl je nog steeds hoge efficiëntie bereikt, maakt het hele trainingsproces veel eenvoudiger en betrouwbaarder.

De discussie benadrukt hoe vooruitgangen in hardware-interconnecttechnologie (de "wegen" tussen chips) de softwarestrategieën die nodig zijn voor efficiënte AI-training fundamenteel kunnen veranderen.

3,47K

Boven

Positie

Favorieten