Argomenti di tendenza

#

Bonk Eco continues to show strength amid $USELESS rally

#

Pump.fun to raise $1B token sale, traders speculating on airdrop

#

Boop.Fun leading the way with a new launchpad on Solana.

Mi sono un po' perso in tutti gli acronimi e il gergo qui, quindi ho fatto spiegare a Claude senza usare acronimi e ora ha tutto perfettamente senso (tldr; larghezza di banda ⟹ semplicità):

Questa è una discussione tecnica affascinante sulla formazione di modelli di linguaggio di grandi dimensioni su larga scala.

La Conversazione Principale

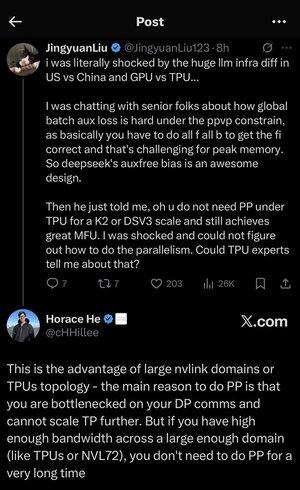

Jingyuan Liu esprime sorpresa nel scoprire che non è necessario utilizzare certe tecniche di ottimizzazione complesse quando si usano i TPU (Tensor Processing Units - i chip AI specializzati di Google) rispetto alle GPU (Graphics Processing Units - tipicamente i chip NVIDIA).

Concetti Tecnici Chiave Spiegati:

Tipi di Hardware:

•GPU (Graphics Processing Unit): Originariamente progettata per la grafica, ora ampiamente utilizzata per l'AI. NVIDIA domina questo mercato.

•TPU (Tensor Processing Unit): Chip progettati su misura da Google specificamente per l'apprendimento automatico.

Strategie di Parallelismo:

Quando si addestrano modelli AI massicci, è necessario suddividere il lavoro tra molti chip. Ci sono diversi modi per farlo:

1. Parallelismo Dati (DP): Ogni chip elabora diversi batch di dati con la stessa copia del modello.

2. Parallelismo Tensoriale (TP): Le operazioni matematiche del modello sono suddivise tra i chip.

3. Parallelismo a Pipeline (PP): Diversi strati del modello sono posizionati su chip diversi, creando una pipeline.

La Sfida Tecnica in Discussione:

Il problema della perdita ausiliaria: Quando si addestrano modelli molto grandi, spesso si aggiungono "perdite ausiliarie" (obiettivi di addestramento aggiuntivi) a strati intermedi per aiutare i gradienti a fluire meglio attraverso la rete. Sotto i vincoli di PPVP (Parallelismo a Pipeline con Partizionamento Variabile), questo diventa complesso perché:

•È necessario fare "tutti f tutti b" (tutti i passaggi in avanti, poi tutti i passaggi all'indietro).

•Questo è impegnativo per l'uso della memoria di picco perché è necessario memorizzare i risultati intermedi.

L'innovazione di DeepSeek: Hanno sviluppato un design "auxfree bias" che apparentemente evita la necessità di queste perdite ausiliarie pur continuando a formare in modo efficace.

La Rivelazione Sorprendente:

L'esperto senior ha detto a Jingyuan che con i TPU a scala K2 o DSV3 (queste sono configurazioni di cluster con centinaia o migliaia di chip), è possibile ottenere un'eccellente MFU (Utilizzo dei FLOPs del Modello - fondamentalmente quanto efficientemente si utilizza l'hardware) SENZA utilizzare il Parallelismo a Pipeline.

Perché è sorprendente?

•Il Parallelismo a Pipeline è tipicamente considerato essenziale per l'addestramento su larga scala.

•È una tecnica complessa che richiede un'ottimizzazione attenta.

•Essere in grado di evitarlo semplifica tutto in modo significativo.

La Spiegazione di Horace He:

Spiega PERCHÉ questo è possibile con i TPU:

Il vantaggio della larghezza di banda: I TPU e i cluster NVIDIA di alta gamma (come NVL72 - l'ultima configurazione a 72 GPU di NVIDIA con interconnessioni NVLink) hanno una larghezza di banda così alta tra i chip che possono gestire i requisiti di comunicazione senza Parallelismo a Pipeline.

L'intuizione chiave:

•Il Parallelismo a Pipeline è principalmente necessario quando sei "bottlenecked su DP comms" (limitato da quanto velocemente puoi comunicare durante l'addestramento parallelo dei dati).

•Se hai abbastanza larghezza di banda su un dominio abbastanza grande (cluster interconnesso), puoi semplicemente utilizzare strategie di parallelismo più semplici.

•Questo funziona "per molto tempo" - il che significa che puoi addestrare anche modelli molto grandi senza raggiungere i limiti.

L'Intuizione:

Pensalo come un sistema autostradale:

•I cluster GPU tradizionali sono come avere strade strette tra le città, quindi hai bisogno di un instradamento complesso (Parallelismo a Pipeline) per evitare ingorghi.

•I cluster TPU o le GPU collegate tramite NVLink sono come avere autostrade enormi - puoi semplicemente inviare tutto direttamente senza un instradamento elaborato.

Questo è un grande affare perché il Parallelismo a Pipeline è complesso da implementare, debug e ottimizzare. Essere in grado di evitarlo pur raggiungendo un'alta efficienza rende l'intero processo di addestramento molto più semplice e affidabile.

La discussione evidenzia come i progressi nella tecnologia di interconnessione hardware (le "strade" tra i chip) possano cambiare fondamentalmente le strategie software necessarie per un addestramento AI efficiente.

3,46K

Principali

Ranking

Preferiti