トレンドトピック

#

Bonk Eco continues to show strength amid $USELESS rally

#

Pump.fun to raise $1B token sale, traders speculating on airdrop

#

Boop.Fun leading the way with a new launchpad on Solana.

私はここでのすべての頭字語と専門用語に少し迷ったので、頭字語を使わずにClaudeに説明してもらいましたが、今ですべてが完全に理にかなっています(tldr; 帯域幅⟹ シンプルさ):

これは、大規模な言語モデルの大規模なトレーニングに関する興味深い技術的議論です。

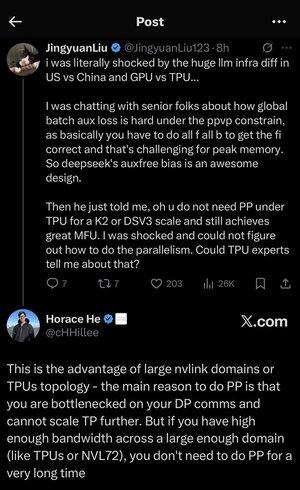

核となる会話

Jingyuan Liu 氏は、TPU (Tensor Processing Units - Google の特殊な AI チップ) と GPU (グラフィックス プロセッシング ユニット - 通常は NVIDIA のチップ) を使用する場合に、特定の複雑な最適化技術が必要ないことを発見して驚きを表明しています。

主要な技術概念の説明:

ハードウェアの種類:

•GPU(グラフィックスプロセッシングユニット):元々はグラフィックス用に設計されましたが、現在はAIに多用されています。NVIDIA はこの市場を支配しています。

•TPU(Tensor Processing Unit):機械学習専用のGoogleのカスタム設計チップ。

並列処理戦略:

大規模な AI モデルをトレーニングする場合、作業を多くのチップに分割する必要があります。これを行うには、いくつかの方法があります。

1データ並列処理(DP):各チップは、同じモデルコピーで異なるバッチのデータを処理します

2テンソル並列処理 (TP): モデルの数学演算はチップ間で分割されます

3パイプライン並列処理(PP):モデルの異なるレイヤーを異なるチップ上に配置し、パイプラインを作成します

議論されている技術的課題:

補助損失の問題: 非常に大規模なモデルをトレーニングする場合、勾配がネットワーク内をより適切に流れるように、中間層に「補助損失」(追加のトレーニング目標)を追加することがよくあります。PPVP (Pipeline Parallelism with Variable Partitioning) 制約では、次の理由でこれが複雑になります。

•「all f all b」(すべてのフォワードパス、次にすべてのバックワードパス)を実行する必要があります。

•これは、中間結果を保存する必要があるため、ピーク時のメモリ使用量では困難です

DeepSeek の革新性: 彼らは、効果的にトレーニングしながら、これらの補助損失の必要性を明らかに回避する「補助フリー バイアス」設計を開発しました。

驚くべき啓示:

上級専門家はJingyuan氏に、K2またはDSV3スケールのTPU(これらは数百または数千のチップを備えたクラスター構成)を使用すると、パイプライン並列処理を使用せずに優れたMFU(モデルFLOP使用率-基本的にハードウェアをどれだけ効率的に使用しているか)を達成できると語った。

なぜこれが驚くべきことなのでしょうか?

•パイプライン並列処理は、通常、大規模なトレーニングに不可欠であると考えられています

•これは複雑な手法であり、慎重な最適化が必要です

•それを回避できるため、すべてが大幅に簡素化されます

ホレス・ヘの説明:

彼は、TPUでこれが可能な理由を次のように説明しています。

帯域幅の利点: TPU とハイエンド NVIDIA クラスター (NVL72 - NVLink 相互接続を備えた NVIDIA の最新の 72 GPU 構成など) は、チップ間の帯域幅が非常に高いため、パイプライン並列処理なしで通信要件を処理できます。

重要な洞察:

•パイプライン並列処理は、主に「DP通信のボトルネック」がある場合に必要です(データ並列トレーニング中の通信速度によって制限されます)

•十分な大きさのドメイン(相互接続されたクラスタ)に十分な帯域幅がある場合は、より単純な並列処理戦略を使用できます

•これは「非常に長い間」機能します - 非常に大きなモデルでも限界に達することなくトレーニングできることを意味します

直感:

高速道路システムのようなものだと考えてください。

•従来のGPUクラスターは、都市間の道路が狭いようなものであるため、交通渋滞を回避するために複雑なルーティング(パイプライン並列処理)が必要です

•TPUクラスターまたはNVLink接続GPUは、巨大なスーパーハイウェイのようなものです - 派手なルーティングなしですべてを直接送信できます

パイプライン並列処理は実装、デバッグ、最適化が複雑であるため、これは大きな問題です。高効率を達成しながらそれを回避できるため、トレーニングプロセス全体がはるかにシンプルで信頼性が高くなります。

このディスカッションでは、ハードウェア相互接続技術 (チップ間の「道路」) の進歩が、効率的な AI トレーニングに必要なソフトウェア戦略をどのように根本的に変えることができるかを強調しています。

3.46K

トップ

ランキング

お気に入り